벨기에 Imec, ASML 차세대 High NA EUV 장비 확보…전 세계 10대 미만

4억 달러 규모 차세대 리소그래피 시스템으로 2nm 이하 공정 개발 가속화, EU 반도체 주권 확보 핵심 인프라로 부상

- •벨기에 반도체 연구소 Imec, ASML의 4억 달러 규모 High NA EUV 리소그래피 장비 확보—전 세계 10대 미만 존재

- •8nm 회로 패턴 구현 가능한 차세대 장비로 2nm 이하 공정 개발 가속화, 2026년 4분기 자격 인증 완료 목표

- •EU 칩스법 지원 25억 유로 NanoIC 파일럿 라인 핵심 설비로, 유럽 반도체 기술 주권 확보 전략의 중심축 역할 기대

유럽 반도체 연구의 중심, 차세대 칩 제조 기술 확보

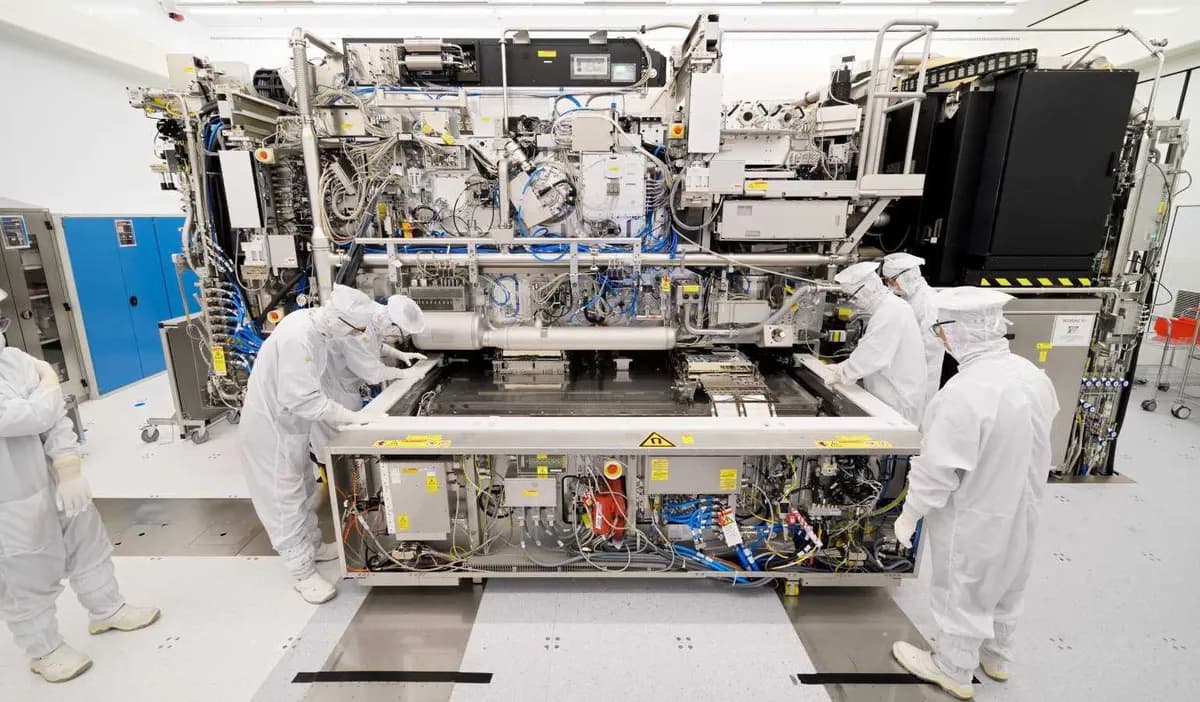

벨기에 반도체 연구 허브 Imec(이멕)이 ASML의 차세대 High NA EUV(극자외선) 리소그래피 장비 'TWINSCAN EXE:5200'을 확보했다고 3월 18일 발표했다. 약 4억 달러(약 5,600억 원) 규모의 이 장비는 현재 전 세계적으로 10대 미만만 존재하는 최첨단 칩 제조 시스템으로, 단일 노광으로 8나노미터(nm) 크기의 회로 패턴을 구현할 수 있다. Imec은 이번 주 초 네덜란드 펠트호번에 위치한 ASML 시설에서 장비를 인수했으며, 벨기에 뢰번 본사의 클린룸에 설치를 완료했다.

Imec CEO 뤽 판 덴 호브(Luc Van den hove)는 "이번 High NA EUV 장비 도입은 유럽의 전략적 독립성과 글로벌 반도체 가치 사슬에서 유럽의 입지를 강화하는 데 필수적"이라고 강조했다. 로이터 보도에 따르면 인텔(Intel)과 SK하이닉스 등 ASML의 주요 고객사들은 2027년부터 High NA 장비를 활용해 차세대 AI 로직 칩과 고대역폭 메모리(HBM) 칩 양산에 나설 계획이다.

왜 이 장비가 중요한가: 2nm 이하 공정 시대의 관문

High NA(High Numerical Aperture, 고개구수) EUV 기술은 기존 Low NA EUV 대비 해상도를 크게 향상시킨 차세대 리소그래피 기술이다. 'NA(개구수)'는 렌즈가 빛을 모으는 능력을 나타내는 지표로, 수치가 높을수록 더 미세한 회로 패턴을 구현할 수 있다. ASML의 EXE:5200은 NA 0.55를 달성해 기존 Low NA EUV(NA 0.33) 대비 약 1.7배 향상된 해상도를 제공한다.

이는 2nm 이하 공정 개발에 필수적인 기술로 평가된다. 현재 삼성전자와 TSMC가 3nm 공정 양산 단계에 있으며, 2nm 공정 개발 경쟁이 치열한 상황에서 High NA EUV는 1.4nm, 1nm 등 차세대 공정 구현의 핵심 도구가 될 전망이다. 특히 AI 반도체 수요 급증으로 고성능·저전력 칩에 대한 요구가 커지면서, High NA EUV의 전략적 가치는 더욱 높아지고 있다.

Imec이 이 장비를 확보한 것은 단순한 연구 인프라 확충을 넘어, 유럽이 미국·아시아와의 반도체 기술 격차를 줄이고 독자적인 칩 제조 생태계를 구축하려는 전략의 일환이다. EU는 '유럽 칩스법(EU Chips Act)'을 통해 2030년까지 글로벌 반도체 시장 점유율을 현재 10%에서 20%로 확대하는 목표를 세웠으며, Imec의 차세대 칩 개발 인프라는 이 목표 달성의 핵심 축이 될 것으로 보인다.

Imec의 역할: 칩 제조업체들의 공동 연구 플랫폼

Imec은 반도체 장비 제조사와 칩 제조업체 간 가교 역할을 하는 독특한 비즈니스 모델을 운영한다. 수백억 원대의 최첨단 장비를 개별 기업이 단독으로 구매하기 어려운 점을 고려해, Imec은 ASML, Applied Materials, LAM Research, KLA, 도쿄일렉트론(Tokyo Electron) 등 주요 장비 업체들과 양자 계약을 맺고 최신 장비를 확보한 뒤, 이를 여러 기업과 연구자에게 공유한다.

이를 통해 글로벌 칩 제조업체들은 Imec의 팹(fabrication facility) 환경에서 차세대 공정 기술을 테스트하고 검증할 수 있다. 실제 양산 라인에 투자하기 전 기술적 타당성을 확인할 수 있어, 개발 위험을 줄이고 시장 출시 시간을 단축할 수 있다. Imec은 EUV 기술 초기 개발 단계부터 ASML과 협력해온 역사가 있으며, 이번 High NA EUV 장비 도입 역시 그 연장선상에 있다.

NanoIC 파일럿 라인: EU의 반도체 주권 프로젝트

High NA EUV 장비는 Imec이 추진 중인 25억 유로(약 3조 7,000억 원) 규모의 'NanoIC 파일럿 라인' 프로젝트의 핵심 설비다. 이 프로젝트는 EU 칩스법에 따라 14억 유로의 공공 자금 지원을 받으며, 2026년 4분기까지 완전한 자격 인증(qualification)을 완료할 계획이다.

NanoIC 파일럿 라인은 단순한 연구 시설이 아니라, 실제 양산 환경에 가까운 조건에서 차세대 공정을 검증하는 '준양산(pilot production)' 라인이다. 이를 통해 유럽 내 팹리스(fabless) 기업들과 파운드리(foundry) 업체들이 2nm 이하 공정 기술을 확보하고, 글로벌 반도체 공급망에서 독자적인 위치를 확보하려는 것이 EU의 전략이다.

현재 첨단 반도체 제조는 TSMC(대만), 삼성전자(한국), 인텔(미국) 3사가 과점하고 있으며, 유럽은 사실상 첨단 로직 칩 제조 능력이 부재한 상황이다. NanoIC 프로젝트는 이러한 기술 종속성을 해소하고, 최소한 파일럿 수준에서라도 차세대 공정 기술을 내재화하려는 시도로 볼 수 있다.

글로벌 High NA EUV 경쟁 현황

| 항목 | Low NA EUV | High NA EUV | 변화 |

|---|---|---|---|

| 개구수(NA) | 0.33 | 0.55 | +67% |

| 최소 선폭 | 13nm | 8nm | -38% |

| 해상도 | 기준 | 1.7배 향상 | +70% |

| 장비 가격 | 약 1.5억 달러 | 약 4억 달러 | +167% |

| 전 세계 설치 대수 | 200대 이상 | 10대 미만 | - |

| 주요 고객사 | TSMC, 삼성, 인텔, SK하이닉스 | 인텔, SK하이닉스, (TSMC 검토 중) | - |

ASML은 High NA EUV 장비를 연간 10~20대 수준으로 제한 생산하고 있으며, 인텔이 첫 고객으로 2대를 확보한 것으로 알려졌다. SK하이닉스는 HBM4 개발을 위해 High NA EUV 도입을 검토 중이며, TSMC는 신중한 입장을 유지하고 있다. Imec의 장비 확보는 이러한 소수 기업 중심 독점 구조에서 유럽이 기술 접근성을 확보했다는 점에서 의미가 크다.

[AI 분석] 반도체 기술 주권 경쟁 심화 전망

Imec의 High NA EUV 확보는 글로벌 반도체 기술 주권 경쟁이 새로운 국면에 접어들었음을 시사한다. 미국은 CHIPS Act를 통해 자국 내 첨단 팹 구축을 지원하고 있으며, 중국은 자체 EUV 기술 개발에 박차를 가하고 있다. 유럽 역시 EU 칩스법과 NanoIC 프로젝트를 통해 기술 독립성 확보에 나서면서, 반도체 공급망의 다극화가 가속화될 가능성이 높다.

다만 유럽이 실제 양산 역량까지 확보하기에는 여전히 넘어야 할 산이 많다. Imec의 파일럿 라인은 연구·개발 목적이 주된 만큼, 이를 상업적 대량 생산으로 전환하려면 수조 원 규모의 추가 투자와 10년 이상의 시간이 필요할 것으로 예상된다. 또한 ASML의 High NA EUV 생산 능력이 제한적인 상황에서, 인텔·TSMC·삼성 등 기존 팹 업체들과의 장비 확보 경쟁도 치열해질 전망이다.

한편 AI 반도체 수요 급증으로 2nm 이하 공정의 상용화 시점이 앞당겨질 가능성도 제기된다. 엔비디아, AMD, 구글 등 AI 칩 설계 기업들은 더 높은 트랜지스터 집적도와 전력 효율을 요구하고 있으며, 이는 High NA EUV 기술의 조기 도입을 촉진하는 요인이 될 것으로 보인다. Imec이 2026년 4분기까지 완전 자격 인증을 완료한다면, 유럽 기업들이 2027~2028년경 차세대 AI 칩 개발 경쟁에 본격 합류할 수 있는 기반이 마련될 것으로 전망된다.

AD

인아티클 광고

댓글 (4)

로그인하고 댓글을 작성하세요

정말 흥미로운 기사입니다. AI 기술의 발전 속도가 놀랍습니다.

동의합니다. 특히 최근 멀티모달 AI의 발전이 눈에 띕니다.

이 분야에 대한 심층 분석 기사가 더 필요합니다. 좋은 기사 감사합니다.

AI 윤리에 대한 논의도 함께 다뤄졌으면 좋겠습니다.